Aug 1st, 2022

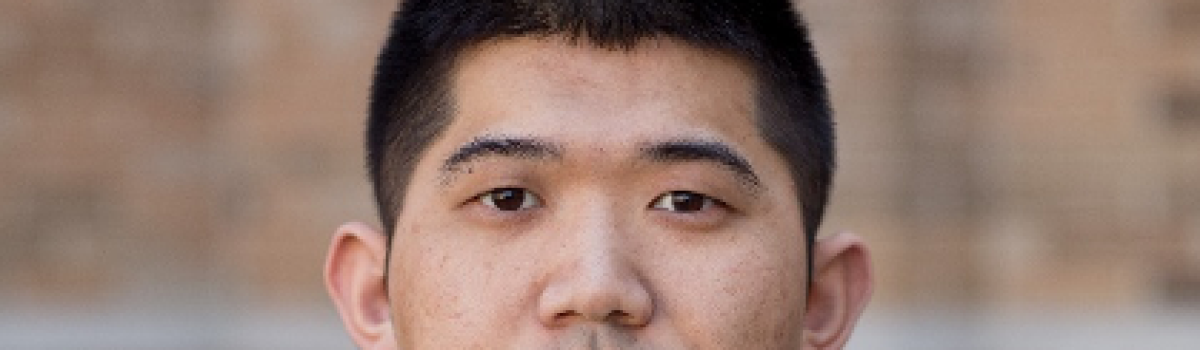

Xunzhao Yin

Assistant Professor

Zhejiang University

Email:

xzyin1@zju.edu.cn

Personal webpage

https://person.zju.edu.cn/en/xunzhaoyin

Research interests

Circuits and architectures based on emerging technologies & computational paradigms; hardware-software co-design & optimization; computing-in-memory & brain-inspired computing; hardware solutions for unconventional computing, etc.

Short bio

Xunzhao Yin (S’16-M’19) is an assistant professor of the College of Information Science and Electronic Engineering at Zhejiang University. He received his Ph.D. degree in Computer Science and Engineering from University of Notre Dame in 2019 and B.S. degree in Electronic Engineering from Tsinghua University in 2013, respectively. His research interests include emerging circuit/architecture designs and novel computing paradigms with both CMOS and emerging technologies. He has published top journals and conference papers including Nature Electronics, IEEE TC, IEEE TCAD, IEEE TCAS, IEEE TED, DAC, ICCAD, IEDM, Symposium on VLSI, etc. He has received the best paper award nomination of ICCAD 2020, DATE2022, etc. He serves as the Associate Editor of ACM SIGDA E-Newsletter, and Review Editor of Frontiers in Electronics.

Research highlights

Prof. Yin’s research interests span across architectures, circuits and devices, his research goal is to develop highly effective solutions that create a bridge between emerging devices and circuit and architecture innovations to develop highly efficient and scalable non-Von Neumann architectures/hardware platforms to address the computational challenges demanded by ML and IoT applications. Towards this goal, Prof. Yin’s work has specifically addressed the design of efficient emerging circuits and architectures that (i) interact with various emerging device technologies, e.g., Ferroelectric FET (FeFET), and (ii) complement non-Von Neumann computational paradigms for computationally-hard optimization problems. Some of his research highlights are summarized below:

Prof. Yin proposed to leverage the merged memory and computation property of FeFET to address the memory wall issues present in the AI inference module based on conventional CMOS architecture, and proposed a series of FeFET based ultra-compact, ultra-low power designs of content addressable memory (CAM) that achieve superior information density and power efficiency for data-intensive search tasks. By extending the search functionality of CAM to similarity metric calculation, his work further improved the hardware efficiency in the context of emerging applications, e.g., few-shot learning, hyperdimensional computing, database query, etc., making CAMs more applicable for various computation domains. Prof. Yin is also quite fascinated with constructing accelerators that embrace novel architectures and technologies, especially the notion of “letting physics do the computation” to achieve higher performance and energy efficiency than traditional digital machines. He developed an analog circuit based hardware system to realize a novel continuous time dynamical system (CTDS) which solves the satisfiability problems (SAT) with drastically reduced hardware time. He is further researching on the potential hardware-software co-design solutions with the help of emerging devices and computing paradigms for solving complex combinatorial optimization problems.